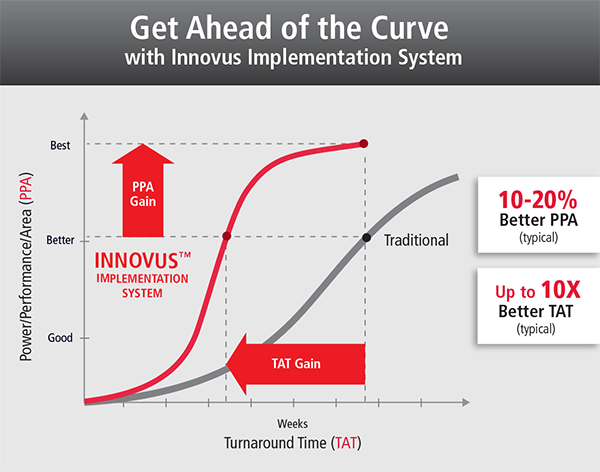

Cadence® Innovus™ Implementation System 针对最具挑战性的设计进行了优化,支持最新的 FinFET 16nm、14 nm、7nm和 5nm工艺,帮助您尽快开始设计,并迅速增加产能。Innovus 系统在组件摆放、优化、布线和时钟设置方面提供了一系列独特的新功能,其体系结构可应对设计流程中的上、下游步骤和影响。这种体系结构最大程度地减少了设计迭代,并可有效改善运行时长,助力产品快速上市。使用 Innovus 系统,您将可以构建风险更低的差异化集成系统。

Innovus 系统提供了多项关键功能。它采用了大规模并行架构,可以处理大型设计,并支持多核工作站上的多线程功能以及计算机网络上的分布式处理。

基于成熟的 NanoRoute ™ 引擎,新一代布线功能基于时序余量和功率,支持可感知布线轨道的时序优化,可尽早解决信号完整性问题并改善布线后的相关一致性。Innovus 系统包括全流程多目标技术,支持同时进行电气和物理优化。它还拥有通用的用户界面,以及附有综合和签核工具的用户命令,从而共享定制化流程。因此,您可以利用强大的报告和可视化功能,提高整个数字流程的设计效率和生产效率。

随着模块的单元数量和复杂性不断增加,需要在布局图中定位的宏的数量也呈爆炸式增长。Innovus 系统提供了混合宏和标准单元摆放功能,可以自动生成宏位置,从而将创建最佳平面图的时间从几天缩短到了几个小时。

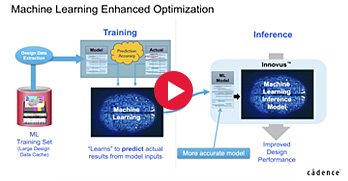

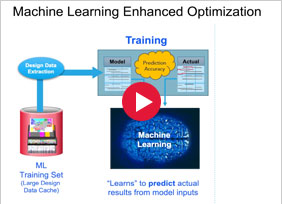

机器学习计算机科学的最新进展与数字实现流程密切相关。Innovus 系统采用了机器学习技术,可为最具挑战性的高性能模块提供最佳 PPA 结果。设计人员可以对机器学习算法的训练进行全方位的控制,以确保算法可以满足其特定的设计要求。

Cadence’s Genus™ Synthesis Solution 与 Innovus 系统紧密集成,可实现从 RTL 综合(synthesis)到实现(implementation)的无缝过渡。借助 GigaPlace ™和GigaOpt ™ 引擎用与 Genus 物理综合的共享摆放和优化技术,该解决方案可为高级节点设计的收敛提供巨大优势。

由于最新的 FinFET 工艺节点中存在电压降,IR 和 EM 约束条件变得越来越重要。Innovus 系统包括全面的可感知电源完整性的组件摆放、优化、时钟树和布线功能,以确保在的实现过程中解决 IR 和 EM 违规问题,而不会影响最终的 PPA 结果。

Cadence 的 Tempus ™Timing Signoff Solution、 Quantus ™ Extraction Solution 以及 Voltus ™ IC Power Integrity Solution 与 Innovus 系统相互集成。通过这种集成,您可以在物理实现的早期阶段对寄生效应、时序、信号和电源完整性影响进行精确建模,并在这些电气指标上实现更快的收敛,从而更有效地完成设计收敛。